這篇文章將會簡介當看到一個硬體 spec 時,怎麼去設計在這個條件下進行最優化的 RTL。我會以之前參加 TSRI 舉辦的 IC 競賽為例進行說明。後續我也規劃分享一些進階的硬體設計知識。

如何優化硬體的 PPA

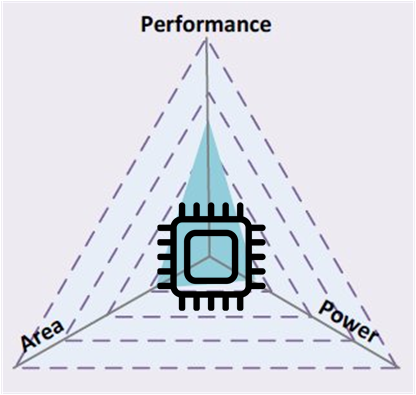

一般常見的評分標準會有(時間、面積、功耗分別簡稱為 T、A、P 值):

- 特定 T 值下,最小化 A 值

- 特定 T 值下,最小化 AT 值

- 特定 A 值下,最小化 P 值

另外還有很多種不同的評分標準。對於這些不同的標準,他可以考驗我們對於硬體的認知。不同的評分標準會對應到架構很不同的設計,我們必須很了解時間、功耗、面積 (Performance, Power, Area; PPA) 三個面向上的取捨。

- 特定 T 下,最優化 A 的文章中特別介紹:特定 T 下,A 最小

- 特定 T 下,最優化 AT 的文章中特別介紹:特定 T 下,AT 最小

如何在設計前估算PPA?

在了解架構的優化會因為評定標準有很大的影響後,我們應該要知道怎麼有效率的在沒有設計前估計 PPA 的數值。依據我的觀察,有很大一部分人的做法是寫完 RTL 並合成後才知道需要多少面積,甚至不了解除法、乘法、加法、暫存器、選擇器之間的面積大小關係。

實例

在介紹完基本技巧後,我會用幾題 IC 競賽的題目,分析我過往的設計想法。這或許並不是最優的解法,但對於各位應該會有所幫助。