這篇文章要介紹如何估計一個硬體架構的面積,這也是一個架構設計最重要的環節。

各元件的面積估計

根據經驗法則,各元件的面積列於下表。這邊的面積大小已經過簡單的正規化,詳細的資料各位可以到 *.lib 檔案中查看。

| 元件 | 面積 |

|---|---|

| 選擇器 (Multiplexer) | 1 |

| 暫存器 (Register) | 10 |

| 加法器 (Adder) | 10 |

例子:乘法器 (Multiplier)

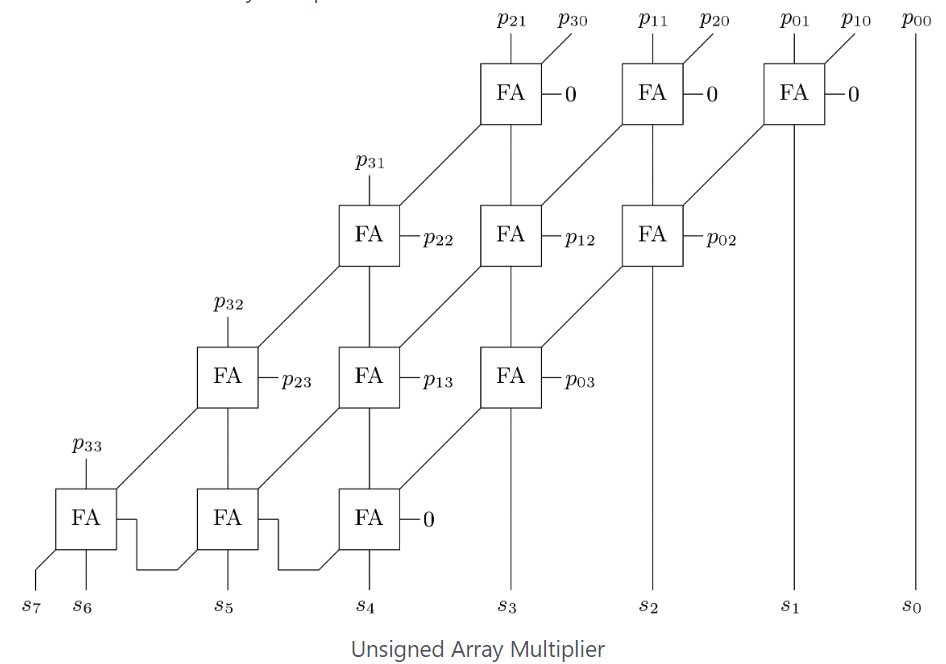

假設我們要設計一個 4-bit 對 4-bit 的乘法器,他的架構會如下圖,總共會需要 12 個加法器。以上面的表來看,他的面積就大約是 120 個選擇器的大小。當然,這邊的全加器 (full adder) 通常可以進一步化簡成半加法器 (half adder)。

另外,通常輸出我們也不會使用到完整的 8-bit,如果是 4-bit 整數輸出,我們只需要 $s_3$ 到 $s_0$,這種情況左下角的 6 個加法器就不需要用到,只留下右上角的 6 個加法器。

而如果是小數的表示法,就會取到中間的幾個 bit。例如:如果輸入的 4-bit 都是 2 位整數和 2 位小數,輸出也是要取 2 位整數和 2 位小數,我們就需要 $s_5$ 到 $s_2$,這樣就只能捨棄最左下角的 1 個加法器,總共需要 11 個加法器。

即使如此,我個人還是會以完整的位數輸出來估算面積。一個原因在於,我們能預留一些 margin。另一個原因在於,通常在架構規模大的時候,我們只需要估測大概的面積即可。依據我的經驗,不管多大的架構,這樣估計的誤差頂多是 2-3 倍。然而,當我們決定不同架構時,他的面積通常就能差距到數十倍。

因此如果是一個 $n$ bit 對 $n$ bit 的乘法器,我會以 $10n^2$ 個選擇器的大小來估計他。