在開始前,我必須說這個題目出得很不好。因為題目規定只要通過他提供的側資即可,並不會有隱藏測資。這次比賽就變成誰最能找到一個 overfit 的方式來完成答案。

題目描述

本題一個波固定為 150 個離散訊號,每個訊號值為 8 bits,其值會介於 0 ~ 255 之間。傳出波 $x(t)$,接收波 $y(t)$,對於存在雜訊的真實世界中的關係式為: $y(t)=Ax(t-d)+n(t)$

其中的變數意義為

$A:$ 衰減率

$n(t)$: 環境雜訊(random noise)

$d$: 兩個波之間相差幾個單位

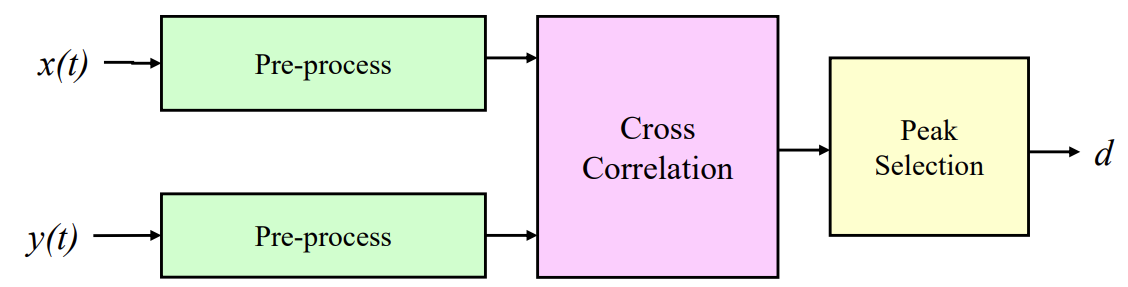

題目建議的演算法是:

- 自行對 $x$ 和 $y$ 做 low pass filter

- 計算 $x$ 和 $y$ 的 cross correlation $R$

- 求 $R$ 最大值的位置

硬體架構圖

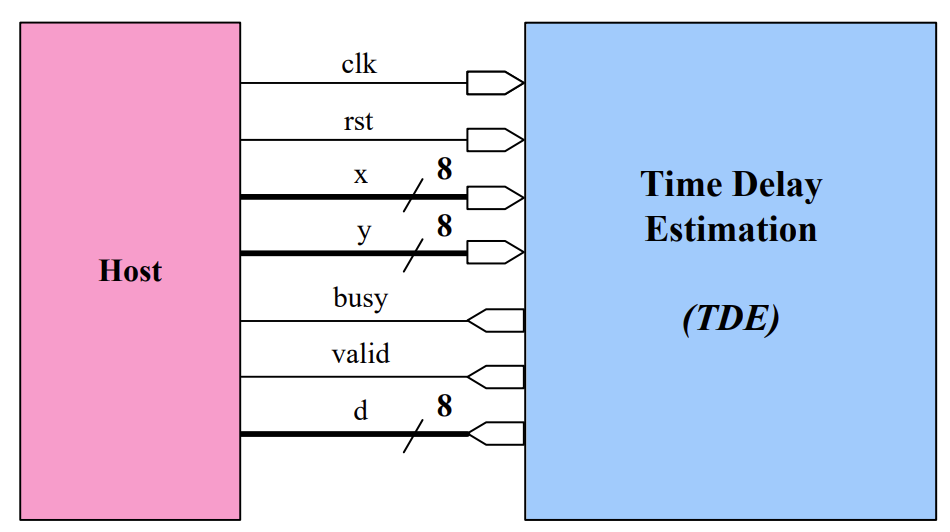

硬體介面描述

| 腳位 | 內容 |

|---|---|

| x, y | 輸入波型數值 |

| busy | 當為 0 時,Host才會輸入資料 x, y |

| d | 輸出距離 d 的資訊 |

| valid | 當 d 值有效時為 1 |

硬體實作

首先,我們觀察到題目提供的波形具有一個很大的波峰。因此,我們先用 MATLAB 找尋最大值的位置,結果就只有 5 個側資沒有通過。而題目又說我們可以 overfit 這些側資,這時候我們就馬上捨棄了題目提供的演算法,想自己尋找新的方法。

在比賽過程中,我們嘗試了各種方式。像是找最大值得前後,最一些簡單處理,但最後就是沒辦法找出一個 overfit 的答案。

最後,我們想出了一個最大減去前 7 個數值作為判斷。最後,我們才發現這個解法事實上就是一種 filtering,而濾波參數$[-1 0 0 0 0 0 1]$。另外,我也發現其他人實作各種不同的參數,如$[1 2 1]$、$[1 2 2 2 1]$。

接下來,我們來分析硬體面積:

A 設計:$[-1 0 0 0 0 0 0 1]$:7 個暫存器、1 個加減法器

B 設計:$[1 2 1]$:2 個暫存器、2 個加減法器、1 個位移器

C 設計:$[1 2 2 2 1]$:4 個暫存器、4 個加減法器、3 個位移器

我們在 A 值估計 的文章中有提到加減法器和暫存器的大小差不多。因此上面的設計在面積上比較是:$C \sim A > B$

競賽細節與心得

這次比賽我認為出題非常失敗,基本上都是在比看誰可以想出一個更好的方法去 overfit。我甚至聽到有人是取一個 threshold,找出大於這個值的第一個點來做判斷,這樣僅僅只需要一個比較器和暫存器即可。我認為過於 overfit 的題目就很難考出硬體設計的能力。